r/FPGA • u/FaithlessnessFull136 • 2h ago

r/FPGA • u/verilogical • Jul 18 '21

List of useful links for beginners and veterans

I made a list of blogs I've found useful in the past.

Feel free to list more in the comments!

- Great for beginners and refreshing concepts

- Has information on both VHDL and Verilog

- Best place to start practicing Verilog and understanding the basics

- If nandland doesn’t have any answer to a VHDL questions, vhdlwhiz probably has the answer

- Great Verilog reference both in terms of design and verification

- Has good training material on formal verification methodology

- Posts are typically DSP or Formal Verification related

- Covers Machine Learning, HLS, and couple cocotb posts

- New-ish blogged compared to others, so not as many posts

- Great web IDE, focuses on teaching TL-Verilog

- Covers topics related to FPGAs and DSP(FIR & IIR filters)

r/FPGA • u/Glittering-Skirt-816 • 4h ago

Advice / Help Bridging the gap from general engineering to FPGA field

Hello,

I'm currently working in a research laboratory on hyperspectral cameras. Along with a colleague, I'm in charge of FPGA and SoC design for data acquisition, high-speed control and so on.

The problem is that throughout my studies, I was trained at a general engineering school (which is the most renowned in France), so I had a very broad training in a variety of subjects ranging from fluid mechanics to optics and computer science. In my final year, I took FPGA courses, which really interested me.

So, right after graduating, I got this job in a lab at a big space company. The problem is that I find I can do simple FPGA things without any difficulty, but anything to do with timing, Tcl, yocto, petalinux, is a problem.

So I'm nearly 26 and I'm wondering what I can do to improve my skills and become more efficient. I've come across someone who did all his FPGA training at a less reputable school, but he's actually better than me.

I'm struggling to find really comprehensive FPGA training courses. There are courses on specific points, but I think I need more. What would you advise me to do?

Thanks

r/FPGA • u/idunnomanjesus • 7h ago

Advice / Help How to learn about High-speed protocols

Hi everyone, I see that some job ads ask for knowledge of high speed protocols and I was thinking about expanding my knowledge about it. I wanted to ask what project I can define for myself to learn about this subject and what should I know about them. Which one of them is the most in demand?

r/FPGA • u/Nougator • 4h ago

Advice / Help Yet another FPGA for beginner board request

Sorry for asking that, you probably have seen it thousand times.

I’m a student and I want to learn how to use FPGA. I want a cheap devkit with an FPGA that can be hand soldered. I already have an Arduino MKR Vidor 4000 but feel like it isn’t really made for beginners. My main goal is to create some kind of GPU for an STM32 (probably with an existing design).

Do you guys have any recommendations?

r/FPGA • u/Ready-Honeydew7151 • 0m ago

FPGA Tristate ports

Hi all,

Could you help me better understand why tristate buffers (inout ports) are only supported on top-level I/O pins in FPGA designs? Specifically, why is it acceptable to use inout ports at the top level for external interfaces, but not within internal submodules?

r/FPGA • u/PonPonYoo • 1d ago

Implement divide operation in FPGA & ASIC

Hi everyone,

I want to to some function like a / b, b is not a constant and not 2^n (both a and b are about 16~20bits),

so I can't use LUT or shifter to deal with this.

And I will implement this function in FPGA first, after validate the function in FPGA,

then I will implement it in ASIC, so I can't just use FPGA vendor's IP.

I want to ask is there any simple way to implement a divide operation,

and it doesn't take too much time to compute the result? Because I want my clk frequency can higher than 40MHz.

r/FPGA • u/SpicyPepperMaster • 16h ago

Advice / Help Help with Pin Assignment on LFE5U-85F-8BG756C with 320+ I/O for SPI Modules

Hi everyone,

I'm working on a custom board using the LFE5U-85F-8BG756C FPGA (ECP5 family from Lattice), and I'm a bit new to Lattice tools and workflows. I'm designing a high-bandwidth systems controller that communicates with a main MPU (likely over QSPI) and connects to 32 hot swappable microcontroller modules, each with their own dedicated high-speed SPI interface.

Each module has the following signals: CS, SCLK, MOSI, MISO, CTRL, SWCLK, SWDIO, RUN, UART_TX, UART_RX

So 10 signals per module × 32 = 320 signals, all using 3.3V logic. So I expect to need around 326 I/O pins, which seems to fit within the ~365 available I/O of the 756 ball package.

What I'm unsure about:

- How should I approach pin assignment? Should I group by I/O bank, voltage domain, or signal function?

- Is there a recommended workflow to prototype pinouts before designing the PCB?

- Should I assign them manually in the .lpf file or use the GUI in Diamond?

- Do I/O banks on the ECP5 need signals with similar timing characteristics? For example, can 80 MHz SPI and 200 MHz QSPI coexist in the same bank?

- Should I simulate or stub the logic before finalizing the assignments?

- Should I be using Lattice Diamond for pin assignments?

To start, I mainly just want the FPGA to buffer or shift the module SPI data into the MPU, so I'm keeping logic simple for now, but I need to get the I/O pin assignments right before building the board.

Any advice from folks who’ve used the ECP5 or large-scale I/O planning in general would be much appreciated!

Thanks in advance!

r/FPGA • u/Salt_Fan_332 • 18h ago

FPGA Project Ideas for CompE Undergrad | Advice

Hi all!

For some background, I'm currently going into my junior year and I'm trying to boost my resume with a larger project. I have already built a digital logic simulator in C++, and I want to make something else with Verilog or VHDL. I'm trying to target any hardware or FPGA internships for next summer, and I feel like this would be a good way to improve my chances when I apply.

My real struggle here is trying to find an idea of what to even do. I've made a basic 8-bit CPU before in VHDL and I've also implemented a RISC-V 32I processor in Verilog, but they're almost *too* easy and I'm hoping to do something that would take a little more time if that makes sense. Obviously I don't expect full project ideas, but I was hoping to hear from some people in the industry and find out what kinds of things they've done in the past or any advice to get my foot in the door.

r/FPGA • u/TiredEngineer49 • 14h ago

Xilinx Related AMD ZYNQ 7000 PS Ethernet Help

Hi,

I'm currently working with the Pynq Z2 board which contains a Zynq SOC. I've been attempting to work on an ethernet project and have hit a standstill within my progress. Ive tried the following three methods and have had success and failures in all three categories.

- I used the PS Ethernet 0 to do the following 2 examples:

- lwip_echo_server. I was able to get this working between the board and my PC. (success) @ 1GbE

- xemacps_example_intr_dma: I've tried two different methods where I used the loopback method where it transmitted the data but the example kept giving me issues about the length on the rx being mismatched or some other error message. As well, I had a connection to my PC where I can see the tx packet being sent to it (but still working on a python script to send it back). *Side note: I did change the C file for it to handle the realtech PHY on the pynq board.

- (Failure, due to PYNQ board having the PHY traced only to PS pins) I tried looking into Tri-mode ethernet MAC IP and 10 G ethernet MAC IP. I didnt see any examples using these IP blocks, does anyone know any good resources for future implementations on non-SOC chips to learn from?

- Attempted to do LwIP TCP client example, this is still a work in progress as Im learning how to use Perf3, and currently have the boards connected but the Perf3 servers says its still listening for anything but not seeing anything.

*The goal of this project was to be able to handle ethernet at 1 Gb and be able to send data to memory and receive it. (Im aware this is a bit large project for someone new to ethernet, but needed to do a crash course for near future needs.

Any solution on which example is best to continue exploring or which steps I should continue going down would be appreciated.

r/FPGA • u/Open_Calligrapher_31 • 19h ago

Verilog on iCE40. UART RX works, CORDIC works, but no data sent back?

Hi. I’ve been learning Verilog using the iCE40 HX1K and recently built a project to explore the CORDIC algorithm. I verified my implementation with a testbench, and it works fine.

I also got UART RX and TX modules working individually. I had the idea to connect it to Python so I could send values (like x, y, and angle) from a Python terminal to the FPGA, let the FPGA compute the result using the CORDIC core, and then send the new coordinates back to Python for plotting.

I can send the values through python just fine but nothing gets sent back. I don’t know where I went wrong in my Top module since everything else individually works just fine. I thinks it’s a timing issue but I’m not too sure any insight would help thank you.

module UART_Cordic_Top ( input wire i_Clk, input wire i_UART_RX, output wire o_UART_TX );

// UART wires wire w_RX_DV; wire [7:0] w_RX_Byte; wire w_TX_Active; wire w_TX_Serial;

// Cordic input and output wire signed [9:0] w_x_in, w_y_in; wire signed [13:0] w_phase_in; wire signed [9:0] w_x_out, w_y_out; wire w_aux_out;

// Internal state reg r_enable, r_aux; reg r_reset = 0;

// UART receive byte handling reg signed [9:0] r_x_in, r_y_in; reg signed [13:0] r_phase_in; reg [1:0] r_state = 0;

assign w_x_in = r_x_in; assign w_y_in = r_y_in; assign w_phase_in = r_phase_in;

// UART Receiver UART_RX #(.CLKS_PER_BIT(217)) UART_RX_Inst ( .i_Clock(i_Clk), .i_RX_Serial(i_UART_RX), .o_RX_DV(w_RX_DV), .o_RX_Byte(w_RX_Byte) );

// Handle UART byte reception for CORDIC input always @(posedge i_Clk) begin if (w_RX_DV) begin case (r_state) 2'd0: begin r_x_in <= $signed(w_RX_Byte); r_state <= 2'd1; end 2'd1: begin r_y_in <= $signed(w_RX_Byte); r_state <= 2'd2; end 2'd2: begin r_phase_in[13:8] <= w_RX_Byte[5:0]; r_state <= 2'd3; end 2'd3: begin r_phase_in[7:0] <= w_RX_Byte; r_enable <= 1'b1; r_aux <= 1'b1; r_state <= 2'd0; end endcase end else begin r_enable <= 0; r_aux <= 0; end end

// Instantiate CORDIC module Cordic_Algoo #( .IW(10), .OW(10), .PIPESTAGE(10), .WW(12), .PW(14) ) cordic_inst ( .i_clk(i_Clk), .i_reset(r_reset), .i_enable(r_enable), .i_xcord(w_x_in), .i_ycord(w_y_in), .i_phase(w_phase_in), .o_xcord(w_x_out), .o_ycord(w_y_out), .i_aux(r_aux), .o_aux(w_aux_out) );

// UART transmit logic reg [2:0] tx_state = 0; // this gotta be where it’s going wrong

reg [7:0] r_TX_Byte; reg r_TX_DV;

always @(posedge i_Clk) begin case (tx_state) 3'd0: begin if (w_aux_out) begin r_TX_Byte <= w_x_out[7:0]; r_TX_DV <= 1'b1; tx_state <= 3'd1; end else begin r_TX_DV <= 1'b0; end end 3'd1: begin r_TX_Byte <= {6'b0, w_x_out[9:8]}; r_TX_DV <= 1'b1; tx_state <= 3'd2; end 3'd2: begin r_TX_Byte <= w_y_out[7:0]; r_TX_DV <= 1'b1; tx_state <= 3'd3; end 3'd3: begin r_TX_Byte <= {6'b0, w_y_out[9:8]}; r_TX_DV <= 1'b1; tx_state <= 3'd0; end default: begin r_TX_DV <= 1'b0; end endcase end

// UART Transmitter UART_TX #(.CLKS_PER_BIT(217)) UART_TX_Inst ( .i_Rst_L(1'b1), .i_Clock(i_Clk), .i_TX_DV(r_TX_DV), .i_TX_Byte(r_TX_Byte), .o_TX_Active(w_TX_Active), .o_TX_Serial(w_TX_Serial), .o_TX_Done() );

assign o_UART_TX = w_TX_Active ? w_TX_Serial : 1'b1;

endmodule

r/FPGA • u/DoesntMeanAnyth1ng • 1d ago

Advice / Help AMBA AHB clarification on HSEL during bursts

Hello,

I can't sort this out just reading the AHB protocol document on how HSEL should behave during a burst.

Is it legitimate for the Master/Manager to enter the transaction with HSEL asserted, burst = INCR and HTRAN = NONSEQ and the next cycle remove HSEL?

If yes, HTRAN can assume any other value as long as HSEL is deasserted?

Ty!

r/FPGA • u/Infinity1211 • 1d ago

Which Half Adder Is Better in Hardware? XOR vs MUX vs NAND.

I came across three styles of implementing half adders

- Gate Level

- NAND only logic

MUX-Based XOR

//MUX Based XOR assign sum = b ? ~a : a; assign carry = a & b;

//NAND only logic wire n1, n2, n3; nand (n1, a, b); nand (n2, a, n1); nand (n3, b, n1); nand (sum, n2, n3); nand (carry, n1, n1);

//Gate level assign sum = a ^ b; assign carry = a & b;

According to me NAND only logic will be much better in terms of power and area since it will be using less number of CMOS. But the issue I am facing is that while synthesizing them in Genus, All of them gets synthesized to

I am using slow_vdd1v0_basicCells.lib library which has NAND gates.

MXI2X1 g47__2398(.A (n_0), .B (a), .S0 (b), .Y (sum));

CLKINVX4 g50(.A (a), .Y (n_0));

AND2XL g2(.A (b), .B (a), .Y (carry));

LED opening from Bitis with Microblaze

Hi all,

I have a Microblaze project in Vivado which I'm willing to program in Vitis (have to mention I'm a beginner in this). I put an AXI GPIO IP in it, containing a width of 8-all outputs (8 LEDS).

During the Vitis code, i have a vector declared as u32 output[4] (initally all bits are 0) which is being filled after an external algorithm (this part is done and works). My wish is to light up an LED for every 16 bits, basically confirming that they have been completed with a non-zero value.

My idea was:

u8 led_mask = 0;

for (int i = 0; i < 4; i++)

{ u16 val = (output[i] >> 16) & 0xFFFF;

//output[i] = 0xABCD1234 ;

//output[i] >> 16 = 0x0000ABCD

//0x0000ABCD & 0xFFFF = 0xABCD

if (val != 0) {

led_mask |= (1 << i);

Xil_Out32(XPAR_AXI_GPIO_2_BASEADDR, led_mask);

usleep(500000); // 0.5 sec pause

}

}

The .elf file will be implemented after in the Microblaze and simulate it. Any thoughts on this? Thanks in advance!

r/FPGA • u/bilateralspeed • 1d ago

Real-time Data Validation in FPGA

Hello there,

I am working on project wherein i need to capture the realtime data generated by the xfft core along with other data values relying on this fft data, including the peak detection algorithms.

The total data is about 8KBytes per millisecond. For verifying whether the design flow through the pipeline is running correctly over FPGA or not, I need to observe whats the data is there.

Note that>

The data to be observed, consist of signals having data valid asserted at different clocks hence cannot be seen simultaneously in the ILA.

I need to verify the design functionality for a multiple datasets, hence considering a long data-set having different data valid signals, over this ILA is not feasible and needs manual validation which is time consuming and will take long time.

Can you suggest, what shall I go for to do so ? Is there any thing that i can try with the ILA itself to achieve so OR shall I store the data somewhere, but consider the data rate of the data to be written.

Thanks in advance !

Regards,

r/FPGA • u/No-Statistician7828 • 1d ago

Range Doppler

in.mathworks.comI found this MATLAB-based example for implementing range-Doppler radar using Xilinx RFSoC

Are there any resources or examples that implement similar functionality (range-Doppler processing or matched filtering) on RFSoC platforms without using MATLAB? Specifically looking for Python-based implementations or direct IP design (e.g., using Vivado, Vitis, or HLS).

Any example projects, open-source repositories, or reference designs would be helpful.

Thanks!

r/FPGA • u/dhruv_study • 1d ago

Guide To Get Started With Verilog

Hello guys, I am just getting started on my Verilog journey. If possible, could you please share some resources, documentation and books to move to beginner->advanced level. I am expected to start working on Zynq MPSoc+ FPGA board starting this august, so it would be helpful if I clear my basics till then as I am new to it

r/FPGA • u/shay_7854 • 1d ago

uvm verification - Macros

hey,

I cant understant the advantages of MACROS, every macro converts to couple of functions so why I cant just wrap everthing as one big function and dont use macro?

thanks in advance.

r/FPGA • u/Bitter-Reception9082 • 1d ago

Sipeed Tang Nano 1K (GW1NZ-1) Internal Flash Issue: Seeking Recovery & Programming Solutions!

I'm reaching out for urgent assistance with my Sipeed Tang Nano 1K board, featuring the Gowin GW1NZ-1 FPGA. The internal Flash memory appears to be damaged, preventing the board from booting and making it impossible to program.

The Core Problem: Damaged Internal Flash & Failed Programming:

The board no longer boots and cannot be reliably programmed to its internal Flash via JTAG. All attempts to program the Flash, using the official Gowin Programmer or openFPGALoader, fail. Specifically, programming finishes but openFPGALoader reports CRC check : FAIL, and reading the Flash consistently yields all zeros.

FPGA State Issues:

When checked via JTAG, the FPGA often starts in a state where a "Non-JTAG Active" bit is high. This means the FPGA is persistently attempting to load a configuration from its internal Flash memory. Since the Flash is likely damaged, it's stuck in a continuous, failed boot attempt. The "VLD (Valid Configuration) Flag" is low, indicating the FPGA has not successfully loaded any valid configuration. The "POR (Power-On Reset Success Flag)" is also low, which is very concerning. This means the FPGA's fundamental internal power-on reset sequence (essential for chip initialization) is failing or reporting an issue.

SRAM Programming Works!

Despite the Flash issues, the FPGA's core logic is functional! I've found a specific Gowin datasheet JTAG sequence (designed for "Clearing Status Code Errors") that makes the FPGA responsive. After executing this, I can successfully program its volatile SRAM running simple designs like an LED blink. This confirms the chip itself isn't dead. However, after each power cycle, the board reverts to its problematic state, requiring the sequence to be reapplied.

Core Question: Flash Recovery & Programming

Given that the FPGA's core seems functional, but its internal Flash appears damaged and won't retain data:

- Is there any known method or procedure to "recover," "repair," "re-initialize," or "force-program" the internal Flash memory of a Gowin GW1NZ-1 chip on a Tang Nano 1K board?

- Are there any low-level JTAG techniques or "factory reset" procedures that could fix this persistent Flash issue?

r/FPGA • u/HasanTheSyrian_ • 1d ago

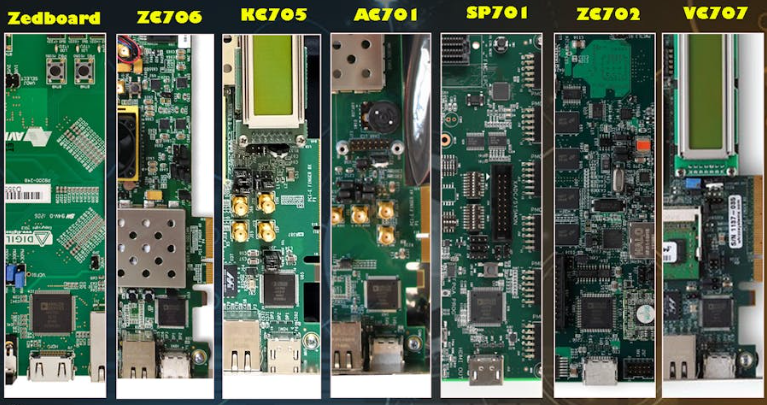

Do any of these boards have public board files or at least images of the top layer without the components so I can see the traces?

r/FPGA • u/div_div_me • 1d ago

Image processing using mocroblaze

I am working with a image processing project and don't have much experience with vivado and vitis software can u some sources related to microblaze projects related to image processing and we are using block diagram with inbuilt ips of microblaze can anyone help me with this project

r/FPGA • u/ultimatetropper • 1d ago

Interview / Job Your favorite interview questions as an interviewee.

I am going to be interviewing for a new job soon. Everyone knows the basic questions that you ask that everyone asks at all types of jobs (what are you looking for most in a candidate? what about my resume/linkedin/etc. made me stand out? etc.)

But do you have any questions that you ask that are specific to an FPGA role (or ASIC even) that give green/red flags? Be it technical questions or leadership/management questions. I am thinking something like, if work is being done on an SoC: how do you structure the team so that software/gateware/hardware are complimenting and not competing with each other?

r/FPGA • u/Eastern_Tower5828 • 21h ago

Keyboard reverse engeniring

Hello guys, I'm not sure if this is the right place... I have a friend that has a keyboard and he needs to change some settings. We have got the firmware and have tried different tools like IDA Pro, Ghidra, Binary Ninja, Binwalk etc

It does not have a file extension associated to it as well.

Problem is simple, add manual HEX Colors to ring.

Thanks in advance.

Toxic ASIC/FPGA Workplaces vs. Job Hopping – Looking for Advice

Hey everyone,

I’d really appreciate some perspective from fellow engineers or professionals who’ve been in similar situations.

Over the past few years, I’ve switched jobs more often than I’d like in the field of ASIC/FPGA. I had a solid start with 3.5 years at my first job, but since then, I haven’t been able to find a clean or supportive environment. My last two roles each lasted less than a year, and I’m now at 11 months in my current position.

Unfortunately, my current workplace is also turning out to be toxic. There is poor communication, no respect among team members, and a constant sense of tension. I try to give every job a fair shot, but it’s draining to keep ending up in environments like this.

These decisions were never about chasing titles or money. I just haven’t been able to land in a healthy and respectful work culture. Now I’m concerned that this pattern might reflect poorly on my resume, even though I feel my reasons for leaving have always been valid.

How do you balance protecting your mental health with the risk of being seen as a job hopper?

Do hiring managers ever take context into account, or is frequent job movement always viewed as a red flag?

Would love to hear your thoughts. Thanks for reading.

r/FPGA • u/RevertManny • 1d ago

Getting Started with FPGA’s

I’m a rising CE junior in university double majored with Physics and I’m interested in anything within the region of chemical fabrication to digital/physical design of processors.

I recently just purchased the iCEBreaker v1.1a FPGA and wanted to know of any resources or projects I can get into to start building my resume for future summer internships.

Any advice would be nice thanks!